University of California, Berkeley EE 42/100

Spring 2010

Prof. A. Niknejad

Final Exam (closed book) Wed•••day, May 12, 2010

Guidelines: Closed book. You may use a calculator. Do not unstaple the exam. In order to maximize your score, write clearly and indicate each step of your calculations. We cannot give you partial credit if we do not understand your reasoning. Feel free to use scratch paper but transfer your final answer to the exam.

Electron charge  $q = 1.60217646 \times 10^{-19} \,\mathrm{C}.$

KCL: Kirchhoff's Current Law states that the net current flow into a node (or super-node or any closed surface) is zero.

$$\sum I_k = 0$$

KVL: Kirchhoff's Voltage Law states that the net voltage drop around any loop is zero.

$$\sum V_k = 0$$

Power flow into a component: (positive means power is absorbed or dissipated.

$$P = I \cdot V$$

Ohm's Law:

$$V = I \cdot R$$

or

$$I = G \cdot V$$

where  $G = R^{-1}$ .

Power dissipated in a resistor:

$$P = I^2 R = V^2 G$$

Resistors in series add:

$$R = R_1 + R_2 + \cdots$$

Conductances in parallel add:

$$G = G_1 + G_2 + \cdots$$

For two resistors in parallel, this implies

$$R_{||} = \frac{1}{\frac{1}{R_1} + \frac{1}{R_2}}$$

When a chain of resistors are in series and connected to a voltage source, the voltage across the kth resistor is given by the voltage divider forma

$$V_k = V_s \frac{R_k}{R_1 + R_2 + \cdots}$$

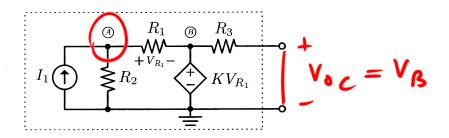

1. (15 points) Consider the following linear circuit consisting of a linear dependent source and an independent current source.

(a) (5 points) Find the open circuit voltage  $V_{oc}$  using KVL. Setup the node equations by using the nodes A and B as shown.

3

(b) (3 points) Find the short circuit current  $(I_{sc})$ . Hint: Try to reuse the above calculation.

$$I_{SC} = \frac{V_{B}}{R_{3}} = \frac{KI_{1}}{(k+1)G_{2}+G_{3}}$$

ISC = VB = KII G3

THE SC DOES NOT CHANGE EITHER

ER FROM PART (4) SWLE WE

DID NOT DO A KCL ON THE

DEPENDENT VOLTAGE SOIRCE

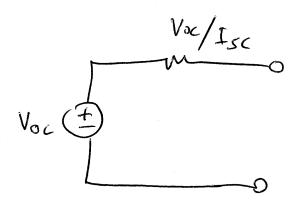

(c) (2 points) Draw the Thevnin Equivalent circuit and label the elements using  $V_{oc}$ and  $I_{sc}$ .

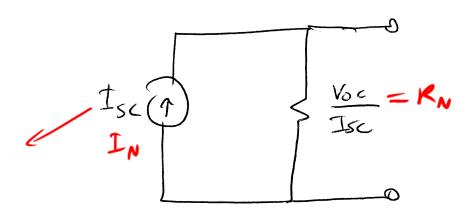

(d) (2 points) Draw the Norton Equivalent circuit and label the elements using  $V_{oc}$  and  $I_{sc}$ .

(e) (3 points) Suppose the circuit is modified as shown below. The dependent source is replaced with an inductor. Using Phasors, find the Norton equivalent impedance directly. You may express your answer using the series and parallel operators.

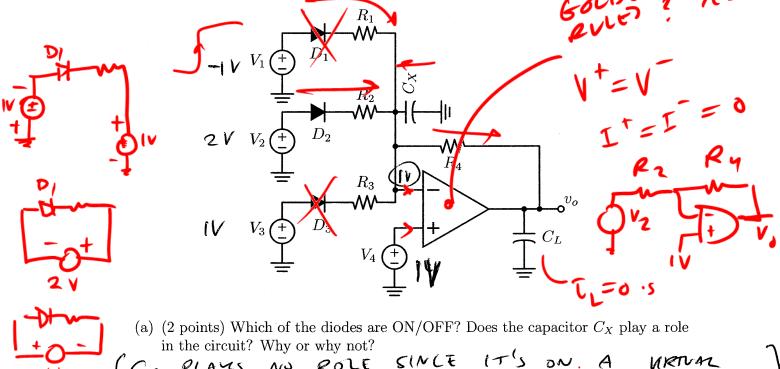

2. (15 points) Consider the following circuit with ideal diodes D1-D3 connected to DC voltage sources. The op-amp is ideal and drives a load capacitor  $C_L = 1\mu F$ .  $R_1 = R_2 = R_3 = R_4 = 1 \text{ k}\Omega$ . Suppose  $V_1 = -1 \text{V}$ ,  $V_2 = 2 \text{V}$ ,  $V_3 = 1 \text{V}$ , and  $V_4 = 1 \text{V}$  and that the capacitor  $C_X$  and  $C_L$  are initially discharged.

(b) (5 points) Use superposition to calculate the  $V_o$  as a function of  $V_1$ ,  $V_2$ ,  $V_3$ , and  $V_4$ .

$$V_{0} = \frac{(V_{2} - V_{4})}{R_{2}} (-R_{4}) + \frac{(V_{3} - V_{4})}{R_{3}} (-R_{4})$$

$$= 1V \cdot (-1) + \delta = -1V$$

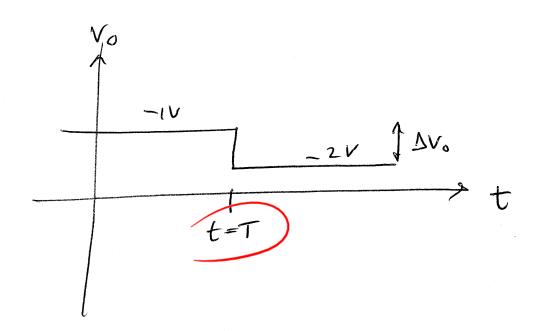

(c) (4 points) Suppose that  $V_1$  then it changes abruptly from -1V to 2V (step function). Draw  $V_o$  as a function of time. (*Hint:* What's the circuit time constant?)

$\Delta V_{\delta} = \frac{\left(V_{1} - V_{4}\right)}{R_{1}} \left(-R_{4}\right) = -1V$

CL CHARGES (NETANSTLY DUE TO

OP-AMP

CY DOES NOT CHANGE

(d) (4 points) Suppose that the voltages are again  $V_1 = -1$ V,  $V_2 = 2$ V,  $V_3 = 1$ V, and  $V_4 = 1$ V and then suppose that  $V_4$  changes abruptly from 1V to 0V (step function). Draw  $V_o$  as a function of time. (*Hint:* What's the circuit time constant?)

DI STILL OFF BUT MORE CURRENTO Froms IN THROUGH V2 & V3

$V_o(t \rightarrow \infty) = -\frac{V_2}{R} = -\frac{V_3}{R} = -\frac{V_3}{R} = -\frac{3V}{R}$

CX MUST DISCHARGE THEWDEST

RESISTANCES IN CIRCUIT.

Reg = R2 | R3 | Ry = 3 452

T = Cx Reg

Reg = Ry = 1hr

SID:

T=CyRay -3V

T 8

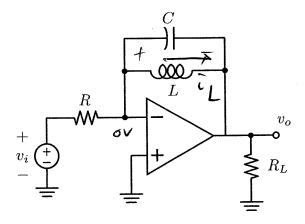

3. (15 points) The circuit shown below has a capacitor C which is initially discharged and an inductor with zero initial current.

(a) (5 points) Write a differential equation describing the circuit behavior. Use  $i_L$  as the unknown quantity.

$$\frac{V_i}{R} = -C \frac{dV_0 + iL}{dt}$$

$$V_0 = -L \frac{diL}{dt}$$

$$\frac{V_i}{R} = LC \frac{d^2iL}{dt^2} + iL$$

NOTE: DIRECTION OF IL MOT SPECIFIED SO DOUBLE CHECK STUDENT'S ANSWER & DEF.

(b) (2 points) What is the circuit Q factor?

(c) (3 points) Express the output voltage  $v_o$  in terms of the inductor current  $i_L$ .

(d) (2 points) If  $L = 1\mu H$ , specify C so that the undamped resonant frequency  $\omega_0$  is equal to 1000 rad/sec.

$$\int_{LC} = \omega_{\delta} = 10^{3}$$

$$\int_{LC} = 10^{6}$$

$$C = \frac{1}{L_{10^{6}}} = \frac{1}{(5^{6}, 10^{6})} = 17^{6}$$

(e) (3 points) Derive  $V_o$  in terms of  $V_i$  directly for a sinusoidal steady-state source. Do this without using the original differential equations with phasor analysis.

$$\frac{V_{i}}{R} = -V_{o} jwC + \frac{V_{o}}{jwL}$$

$$= V_{o} \left( \frac{1}{jwL} - jwC \right)$$

$$\frac{V_{o}}{V_{i}} = \frac{1}{R(1+w^{2}LC)}$$

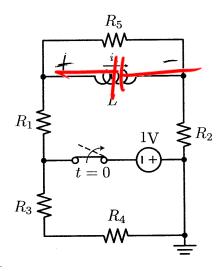

4. (15 points) In the following circuit, the switch has been closed for a long time. It opens at time t=0s.

(a) (5 points) At time  $t = 0^-$ s, right before the switch opens, what's the inductor current  $i_L$ ?

$$i_{L}(t=\bar{0}) = \frac{-1V}{R_{1}+R_{2}}$$

(b) (5 points) Derive the equivalent Thevenin circuit for time  $t \ge 0$ s as seen by the inductor. In other words, what's the equivalent circuit seen by the inductor?

$$V_{th} = V_{oc} = \frac{R_5}{R_1 + R_2 + R_5} (-IV)$$

$$R_{th} = R_5 / (R_1 + R_2)$$

$$CHECH,$$

$$STUDENT'S$$

$$SIGN$$

$$CONVENTION$$

(c) (2 points) What is the circuit time constant (by inspection of the equivalent circuit)?

(d) (3 points) Find the complete solution  $i_L(t)$  for  $t \geq 0$ .

$$i_{L}(0) = \frac{-1\nu}{R_{1}+R_{2}}$$

$$i_{L}(\infty) = 0$$

$$i_{L}(t) = A + Be^{-t/\tau}$$

$$i_{L}(0) = A + B = \frac{-1\nu}{R_{1}+R_{2}}$$

$$i_{L}(\infty) = A = 0$$

$$B = -\frac{1\nu}{R_{1}+R_{2}}$$

$$i_{L}(t) = \frac{-1\nu}{R_{1}+R_{2}}$$

$$i_{L}(t) = \frac{-1\nu}{R_{1}+R_{2}}$$

5. (15 points) Consider the following truth table for a three-input function, with inputs A, B, and C and one output Y.

| A | В | $\mathbf{C}$ | Y   |

|---|---|--------------|-----|

| 0 | 0 | 0            | 1   |

| 0 | 0 | 1            | 1   |

| 0 | 1 | 0            | 0 ← |

| 0 | 1 | 1            | 0   |

| 1 | 0 | 0            | 1   |

| 1 | 0 | 1            | 0   |

| 1 | 1 | 0            | 1   |

| 1 | 1 | 1            | 1   |

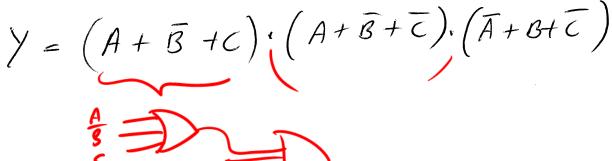

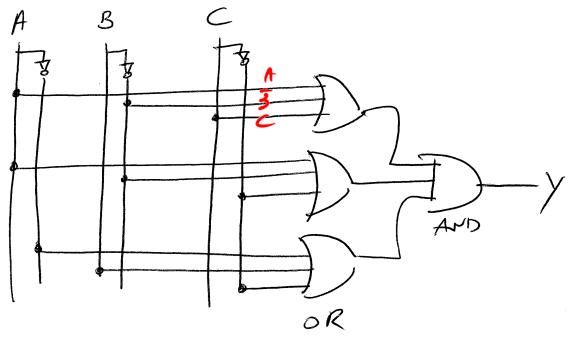

(a) (4 points) Write a Boolean epxpression for Y in maxterm form. In other words, write Y as a product of sums.

(b) (3 points) Implement the logic expression using AND, OR and NOT.

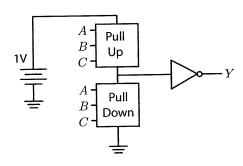

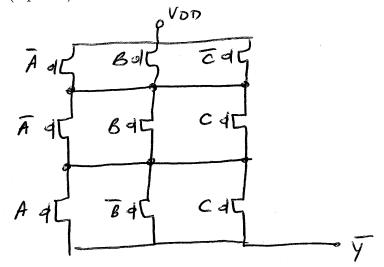

(c) (4 points) Now realize this function using CMOS logic transistors directly as shown above. Draw only the pull down network for  $\overline{Y}$ .

$$\overline{Y} = \overline{(A+\overline{B}+c)} + \overline{(A+\overline{B}+c)} + \overline{(A+B+c)} + \overline{(A+B+c)} = \overline{A} + \overline{B} + \overline{C} + \overline{A} + \overline{B} + \overline{C} + \overline{A} + \overline{C} + \overline{C}$$

(d) (4 points) Draw the pull up network for  $\overline{Y}$ .

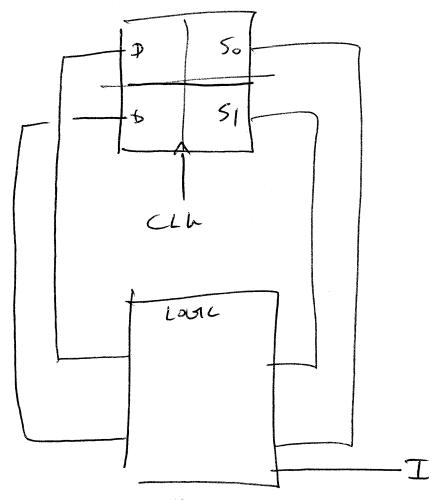

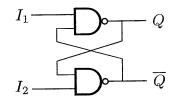

6. (10 points) The following sequential circuit has two inputs  $I_1$  and  $I_2$  and two outputs Q and  $\overline{Q}$ .

(a) (3 points) Complete the truth table where  $Q_n$  is the current output and  $Q_{n-1}$  is the previous output.

| $I_1$ | $I_2$ | $Q_n$ | $\overline{Q}_n$ |

|-------|-------|-------|------------------|

| 0     | 0     | Í     | 1                |

| 0     | 1     | 1     | O                |

| 1     | 0     | O     | ì                |

| 1     | 1     | Qn-1  | Qu-1             |

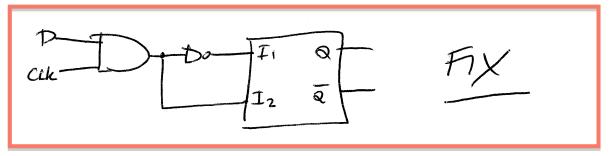

(b) (3 points) Design a D latch using this building block with a clock enable input.

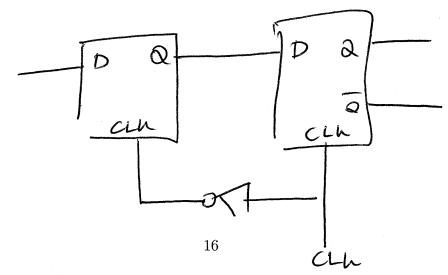

(c) (4 points) Design a positive edge triggered flip-flop using the D latch as a building block.

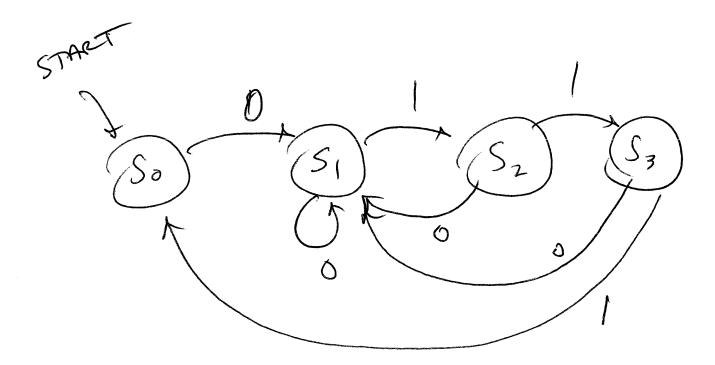

7. (5 points) Draw the state transition diagram for an FSM that detects the patter 011.

S: NO PATTERN

S, : 0

5,:01

53:011

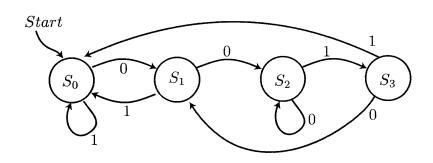

8. (10 points) Consider the following state diagram. There is only one binary input.

(a) (2 points) What pattern does it detect?

001

(b) (2 points) For the pattern "0111100010" write the sequence of states for the system.

$S_1$   $S_0$   $S_0$   $S_0$   $S_0$   $S_1$   $S_2$   $S_2$   $S_3$   $S_1$   $S_0$   $S_0$

(d) (2 points) Implement the state transition logic.

$$S_{0}' = \bar{S}_{1} \bar{S}_{0} \bar{I} + S_{1} \bar{S}_{0} \bar{I} + S_{1} \bar{S}_{0} \bar{I}$$

$S_{1}' = \bar{S}_{1} \bar{S}_{0} \bar{I} + \bar{S}_{1} \bar{S}_{0} \bar{I} + \bar{S}_{1} \bar{S}_{0} \bar{I}$

(e) (2 points) Draw a complete FSM using registers and the logic at the block diagram level.